Tugas Pendahuluan I Modul II

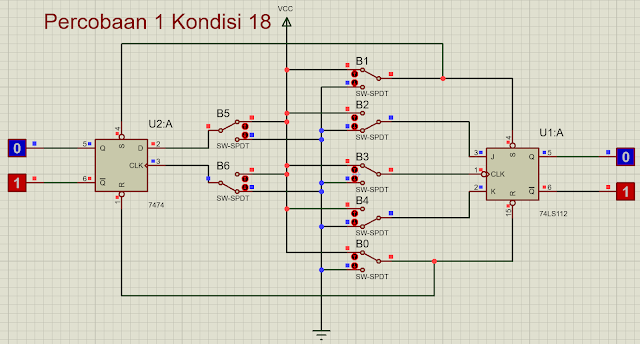

Percobaan I Kondisi 18

1. Kondisi [Kembali]

Buatlah rangkaian J-K flip flop dan D flip flop seperti pada gambar pada percobaan 1 dengan ketentuan input B0 = 1, B1 = 1, B2 = don't care, B3 = don't care, B4 = 0, B5 = don't care, B6 = don't care LED diganti logicprobe

2. Gambar Rangkaian Simulasi [Kembali]

|

| Gambar 1. Gambar Rangkaian |

4. Prinsip Kerja Rangkaian [Kembali]

Sesuai pada kondisi rangkaian memiliki J-K flip flop dan D flip flop dengan inputan berupa saklar SPDT dan output berupa logicprobe.

Pada rangkian ini output dari ke dua buah flip flop berlogika 0 (pada Q) hal ini karena pada inputan J di J-K flip flop berlogika 0 apabila kita ubah menjadi logika 1 maka akan berubah menjadi 1 sedangkan nilai pin S dan pin R berlogika 1 akan tetapi karena pada pin itu berjenis aklif low maka yang terbaca oleh ic pin itu berlogika 0. oleh sebab itu output Q berlogika 0. sedangkan pada D flip flop output juga berlogika 0 pada Q. hal ini karena untuk mengubah output dibutuhkan triger rise time pada pin CLK dan pada pin D harus berlogika 1. dapat dilihat dari gambar bahwa CLK berlogika 0 tanpa diberi trigger hal itulah kenapa output Q berlogika 0.

Saklar SPDT jika tersambaung dengan VCC maka input berlogika 1 dan apabila disambungkan dengan GND maka berlogika 0.

Sedangkan untuk tabel kebenaran dari masing masing IC adalah sebagai berikut:

1. 7474 ( D flip flop ).

Gambar 2. Tabel kebenaran D flip flop

Dapat dilihat pada tabel bahwa ketika clock diberi rise time/proses perubahan dari angka 0 ke 1 dan D berlogika 1 disitulah baru output Q berubah menjadi 1 sedangkan jika D berlogika 0 dan diberikan rise time makan Q akan berubah menjadi logika 0.

2. 74LS112 ( J-K flip flop ).

Gambar 3. Tabel kebenaran J-K flip flop

Dapat dilihat pada gambar terdapat 4 buah kondisi yaitu Q bernilai 1 dan 0 lalu ada kondisi tidak berubah dan toggle atau keadaan berlawanan. dapat kita ketahui logika pada J sebanding dengan logika pada Q ketika J berlogika 1 maka Q berlogika 1 akan tetapi hal itu dapat berubah ketika memasuki kondisi toggle.

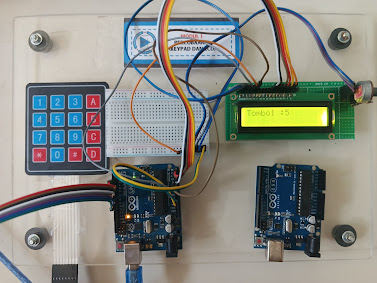

᭒ Aplikasi↠ klik disini

᭒ Gambar Rangkaian↠ klik disini

᭒ Video Percobaan↠ klik disini

᭒ Datasheet 7474 (D flip flop)↠ klik disini

᭒ Datasheet 74LS112 (J-K flip flop)↠ klik disini

Komentar

Posting Komentar