Modul IV

Modul IV

Shift Register & Seven Segment

1. Tujuan [Kembali]

- Merangkai dan menguji Shift Register

- Merangkai dan menguji aplikasi Shift Register pada Seven Segment

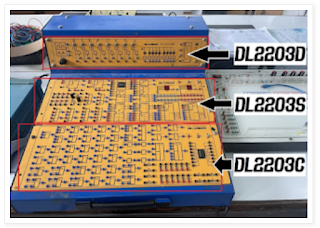

- Panel DL 2203C

- Panel DL 2203D

- Panel DL 2203S

- Jumper

3. Dasar Teori [Kembali]

Shift Register

Register geser (shift register) merupakan salah satu piranti fungsional yang banyak digunakan dalam sistem digital. Tampilan pada layar kalkulator dimana angka bergeser ke kiri setiap kali ada angka baru yang diinputkan menggambarkan karakteristik register geser tersebut. Register geser ini terbangun dari flip-flop. Register geser dapat digunakan sebagai memori sementara, dan data yang tersimpan didalamnya dapat digeser ke kiri atau ke kanan. Register geser juga dapat digunakan untuk mengubah data seri ke paralel atau data paralel ke seri. Ada empat tipe register yang dapat dirancang dengan kombinasi masukan dan keluaran dan kombinasi serial atau paralel :

1. Serial in serial out (SISO)

Pada register SISO, jalur masuk data berjumlah satu dan jalur keluaran juga berjumlah satu. Pada jenis register ini data mengalami pergeseran, flip flop pertama menerima masukan dari input, sedangkan flip flop kedua menerima masukan dari flip flop pertama dan seterusnya.

Gambar 4.1 Serial In Serial Out

2. Serial in paralel out (SIPO)

Register SIPO, mempunyai satu saluran masukan saluran keluaran sejumlah flip flop yang menyusunnya. Data masuk satu per satu (secara serial) dan dikeluarkan secara serentak (secara paralel). Pengeluaran data dikendalikan oleh sebuah sinyal kontrol. Selama sinyal kontrol tidak diberikan, data akan tetap tersimpan dalam register.

3. Paralel In Serial Out (PISO)

Register PISO, mempunyai jalur masukan sejumlah flip flop yang menyusunnya, dan hanya mempunyai satu jalur keluaran. Data masuk ke dalam register secara serentak dengan di kendalikan sinyal kontrol, sedangkan data keluar satu per satu (secara serial).

4. Paralel In Paralel Out (PIPO)

Register PIPO, mempunyai jalur masukan dan keluaran sesuai dengan jumlah flip flop yang menyusunnya. Pada jenis ini data masuk dan keluar secara serentak.

Gambar 4.4 Paralel In Paralel Out

Seven Segment

Piranti tampilan modern disusun sebagai pola 7-segmen atau dot matriks. Jenis 7segmen, sebagaimana namanya, menggunakan pola tujuh batang yang disusun membentuk angka 8 seperti ditunjukkan pada gambar 3.1. Menurut kesepakatan, huruf-huruf yang diperlihatkan dalam Gambar 3.1 ditetapkan untuk menandai segmen-segmen tersebut. Dengan menyalakan beberapa segmen yang sesuai akan dapat diperagakan digit-digit dari 0 sampai 9, juga bentuk huruf A sampai F (heksadesimal).

Sinyal input dari switches tidak dapat langsung dikirimkan ke peraga 7segmen, sehingga harus menggunakan decoder BCD ke 7-segmen sebagai antar muka. Decoder ini terdiri dari gerbang-gerbang logika yang masukannya berupa digit BCD dan keluarannya berupa saluran-saluran untuk mengemudikan tampilan 7-segmen.

Gambar 4.6 Rangkaian Seven Segment Common Anoda

Komentar

Posting Komentar