Tugas Akhir II Modul II

Laporan Akhir

Percobaan 2 Modul 2

1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

1. JK flip flop (74LS112)

|

| Gambar 1. 74LS112 |

2. Saklar SPDT

|

| Gambar 2. Saklar SPDT |

3. Power

|

| Gambar 3. Power DC |

4. Resistor

|

| Gambar 4. Resistor |

5. LED

|

| Gambar 5. LED |

3. Rangkaian [Kembali]

|

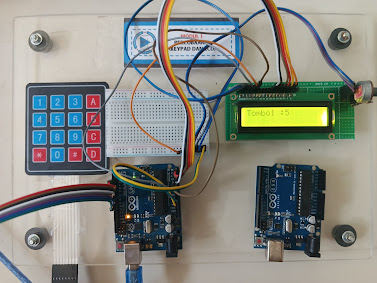

| Gambar 6. rangkaian simulasi |

4. Prinsip Kerja Rangkaian [Kembali]

5. Video Rangkaian [Kembali]

6. Analisa [Kembali]

1. Apa yang terjadi jika input T diberi logika 0 (Low)?

Jawab:

Jika T= 0, T flip flop akan tetap dengan output sebelumnya T flip flop hanya berubah menjadi toggle disaat T = 1 dan diberi trigger maka diketahui saat T = 0 maka output tidak akan berubah.

2. Apa perbedaan ketika input clock T flip flop diberi input rise time dan fall time?

Jawab:

Setiap clock berubah menjadi 0 & 1 sesuai jenis pin dari CLK apa bila berjenis aktif low maka setiap kali terjadi fall time output akan berubah dikarenakan T= 1 maka kondisi memasuki kondisi toggle yang akan berubah terus outputnya secara berlawanan.

7. Link Download [Kembali]

᭒ HTML↠ klik disini

᭒ Aplikasi↠ klik disini

᭒ Gambar Rangkaian↠ klik disini

᭒ Video Percobaan↠ klik disini

᭒ Datasheet 74LS112 (J-K flip flop)↠ klik disini

Komentar

Posting Komentar