Tugas Pendahuluan I Modul III

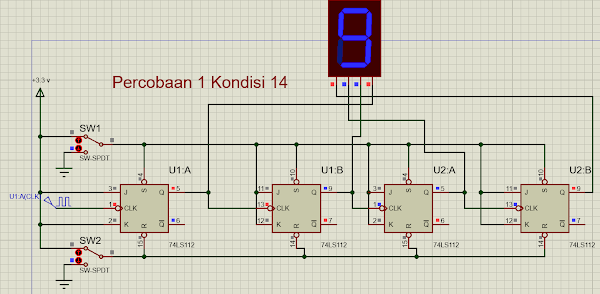

Percobaan I Kondisi 14

1. Kondisi [Kembali]

Buatlah rangkaian seperti gambar percobaan 1 dengan dengan sumber 3.3V dengan output Seven segment

2. Gambar Rangkaian Simulasi [Kembali]

4. Prinsip Kerja Rangkaian [Kembali]

Sesuai pada kondisi rangkaian sudah sesuai dengann rangkaian 1 percobaan 1 modul 3 dengan inputnya diubah menjadi 3,3v dan output disambungkan dengan seven segment.

Pada rangkian ini output akan terus berubah karena rangkaian ini adalah rangkaian counter up dimana dia menghitung sinyal pulsa dan terus meningkat, kita menggunakan 4 buah T flip flop dimaka ketika T = 1 dan diberi trigger pada pin CLK maka output akan mengalami toggle/berlawanan dengan output sebelumnya. sedangkan output T flip flop pertama memasuki pin CLK pada T flip flop kedua dan seterusnya hinggak T flip flop terakhir, maka akan terbuat counter up dimana setiap terdapat perubahan dari logika 1 ke logika 0 ( Fall time ) pada masing masing pin CLK maka output akan toggle.

Output dari T flip flop pertama adalah LSB atau less significant bit dimana itu adalah bit yang memiliki nilai paling dikit sedangkan T flip flop paling kanan / ke 4 adalah MSB atau most significant bit, Oleh karena itu output dari T flip flop pertama disambung pada pin paling kanan di seven segment dan seterusnya.

Saklar SPDT jika tersambaung dengan VCC maka input berlogika 1 dan apabila disambungkan dengan GND maka berlogika 0.

᭒ Aplikasi↠ klik disini

᭒ Gambar Rangkaian↠ klik disini

᭒ Video Percobaan↠ klik disini

᭒ Datasheet 74LS112 (J-K flip flop)↠ klik disini

Komentar

Posting Komentar