Tugas Pendahuluan I Modul IV

Percobaan I Kondisi 6

1. Kondisi [Kembali]

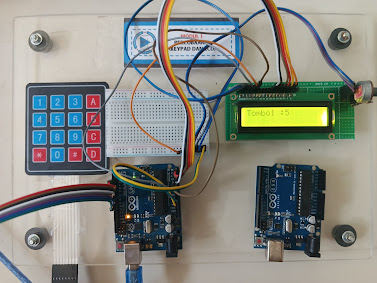

Buatlah rangkaian seperti gambar percobaan 1 dengan menggunakan D flip flop dan output seven segment common katoda.

2. Gambar Rangkaian Simulasi [Kembali]

|

| Gambar 1. Rangkaian Simulasi |

4. Prinsip Kerja Rangkaian [Kembali]

Sesuai pada kondisi rangkaian sudah sesuai dengann rangkaian 1 percobaan 1 modul 4 dengan JK flip flop diubah menjadi D flip flop dan outputnya dihubungkan dengan seven segment common katoda.

Saklar SPDT jika tersambung dengan VCC maka input berlogika 1 dan apabila disambungkan dengan GND maka berlogika 0.

Pada rangkian ini merupakan percobaan shift register dimana ketika SW6 dihubungkan dengan VCC maka output pada D flip flop pertama berubah menjadi 1 dan akan membuat rantaian perubahan pada output D flip flop setelahnya secara satu persatu itu merupakan Serial In karena data yang masuk pada shift register masuk satu persatu. Setelah semua output menjadi 1 lalu kita mengubah SW6 dengan menghubungkannya dengan GND maka output D flip flop pertama akan berubah menjadi 0 dan membuat rantaian perubahan pada output D flip flop setelahnya hal ini dinyatakan sebagai Serial Out karena data keluar dari shift register satu per satu. Oleh sebab itu ketika SW1 hingga SW4 berlogika 1 dan kita mengatur SW6 maka rangkaian menjadi Serial In Serial Out (SISO).

Ketika SW1 - SW4 berlogika berurutan 1010 maka data yang kita miliki adalah 1010 disaat kita jalankan secara keseluruhan data langsung masuk kedalam shift register hal ini dinamakan Paralel In sedangkan disaat keluar dari shift register ke 4 D flip flop mengeluarkan output secara satu persatu hal ini yang membuat dikatakan Serial Out oleh sebeb itu dengan kondisi yang seperti itu rangkaian berubah dari SISO menjadi Paralel In Serial Out (PISO).

᭒ HTML↠ klik disini

᭒ Aplikasi↠ klik disini

᭒ Gambar Rangkaian↠ klik disini

᭒ Video Percobaan↠ klik disini

᭒ Datasheet 7474 (D flip flop)↠ klik disini

᭒ Datasheet 74LS47 (Decoder BCD to Seven Segment)↠ klik disini

Komentar

Posting Komentar