Tugas Akhir I Modul IV

Laporan Akhir

Percobaan 1 Modul 4

1. Jurnal [Kembali]

2. Alat dan Bahan [Kembali]

1. Module D'Lorenzo

2. Jumper

3. Rangkaian [Kembali]

|

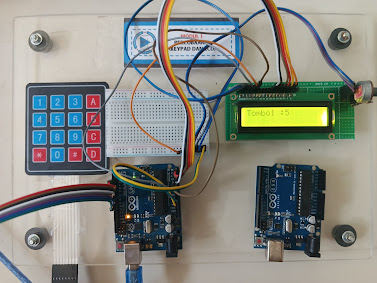

| Gambar 1. Rangkaian Simulasi |

4. Prinsip Kerja Rangkaian [Kembali]

5. Video Rangkaian [Kembali]

6. Analisa [Kembali]

1.) Analisa output yang dihasilkan tiap-tiap kondisi

Jawab:

Kondisi pertama, Rangkaian menjadi jenis SISO karena data yang masuk pada shift register bergerak / bergeser satu persatu dan juga ketika data keluar dari shift register bergeser satu persatu.

Kondisi kedua, rangkaian menjadi jenis SIPO karena data yang masuk pada shift register bergeser satu persatu sedangkan ketika data keluar dari shift register secara bersamaan.

Kondisi ketiga, rangkaian menjadi PISO karena data yang masuk pada shift register secara bersamaan sedangkan ketika data keluar dari shift register secara satu persatu.

Kondisi Keempat, rangkaian menjadi PIPO karena data yang masuk dan keluar dari shift register bergeser secara bersamaan.

2.) Jika gerbang AND pada rangkaian dihabus, sumber clock dihubungkan langsung ke flip flop, bandingkan output yang didapatkan

Jawab:

Hal yang terjadi adalah hilangnya kemampuan rangkaian menjadi tipe Paralel Out dikarenakan yang membuat rangkaian menjadi Paralel Out itu diatur oleh B2 yang dihubung pada gerbang AND jika B2 tidak dihubungkan maka tidak dapat membuat menjadi Paralel Out.

7. Link Download [Kembali]

᭒ Rangkaian↠ klik disini

᭒ Gambar Rangkaian↠ klik disini

᭒ Video Percobaan↠ klik disini

᭒ Datasheet 74111 (JK Flip Flop)↠ klik disini

Komentar

Posting Komentar